**The ADSP-21061LKS-176: A Deep Dive into SHARC's Flagship Floating-Point DSP**

In the realm of digital signal processing, few processor families have achieved the legendary status of Analog Devices' SHARC series. At the pinnacle of this esteemed line stood the **ADSP-21061LKS-176**, a component that not only defined an era of high-performance audio and military/aerospace applications but also continues to be a benchmark for floating-point capability. This deep dive explores the architecture and legacy of this remarkable DSP.

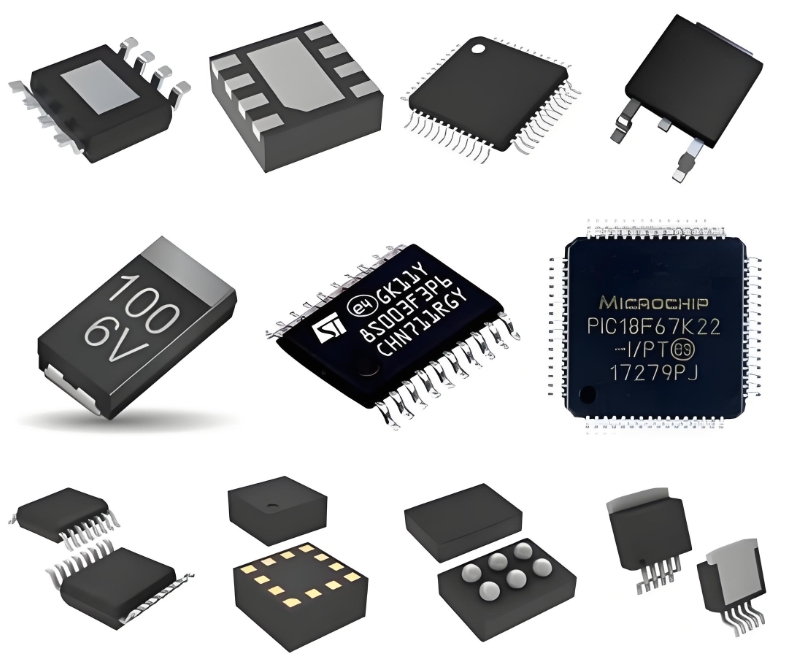

The "LKS" suffix denotes a premium, industrial-temperature grade version of the ADSP-21061, and the "-176" indicates its 176-pin Low-Profile Quad Flat Pack (LQFP) package. This packaging was crucial for designs requiring high component density and reliability in demanding environments. At its core, the ADSP-21061 is built upon a **super-Harvard architecture**, a significant evolution of the traditional Harvard architecture that separates memory into distinct banks for simultaneous instruction and data access. SHARC takes this further with multiple internal buses, allowing for an unprecedented three data transfers per cycle.

A key to its performance is the **on-chip dual-ported SRAM**, which can be configured as either 2M bits of program memory or a combination of program and data memory. This dual-ported nature allows concurrent access by the core and by I/O controllers or other processors in a multiprocessing system, eliminating a common bottleneck. The '21061 excels in multiprocessing; its built-in **link ports and bus arbitration logic** enable the seamless creation of large, scalable DSP arrays without external glue logic. This made it a favorite for complex, computationally intensive systems like sonar array processing and professional audio mixing consoles.

The computational heart of the ADSP-21061 is its 32-bit IEEE floating-point unit. This ensures high dynamic range and eliminates the scaling concerns inherent in fixed-point processors, simplifying algorithm development. The core can execute a single-instruction multiply-accumulate (MAC) operation every cycle, while also performing a memory access. With a cycle time of 25ns (40 MHz) for the -176 speed grade, this translates to a peak throughput of **40 MFLOPS**, a formidable figure in its heyday.

Beyond raw number crunching, its integrated peripherals made it a complete system-on-chip solution. It featured a serial port, a programmable timer, and most notably, a **high-bandwidth parallel I/O port**. This parallel port was incredibly versatile, supporting both multiprocessor interfaces and glueless connection to standard processors like those from the x86 family.

The combination of robust floating-point math, elegant multiprocessing support, and strong I/O capabilities cemented the ADSP-21061L's role in mission-critical and high-fidelity applications. It became the processor of choice for aerospace and defense systems, medical imaging equipment, and the highest-end audio processors where sound quality was non-negotiable.

**ICGOOODFIND**: The ADSP-21061LKS-176 was more than just a chip; it was a complete solution that empowered a generation of engineers to tackle the most complex signal processing challenges. Its balanced architecture of raw computational power, intelligent memory design, and innovative inter-processor communication set a standard for what a high-end floating-point DSP should be, leaving an indelible mark on the industry.

**Keywords**:

* **SHARC Architecture**

* **IEEE Floating-Point**

* **Multiprocessing**

* **Dual-Ported SRAM**

* **Link Ports**